作者: 深圳市昂洋科技有限公司发表时间:2025-12-10 14:12:21浏览量:412【小中大】

要降低顺络CC1206KKX7RBBB104电容(假设为X7R材质1206封装电容,容量0.1μF,常见于高频电路)的高频损耗,需从材料特性、结构设计、工艺优化及电路应用四个层面综合改进,具体措施如下:

一、材料选择:低损耗介质与电极优化

采用NP0/C0G替代X7R(若条件允许)

X7R材质虽温度稳定性较好,但高频损耗(tanδ)通常高于NP0/C0G。NP0/C0G材质的介电损耗可低至0.1%以下,温度系数±30ppm/℃,适合高频振荡、耦合等场景。若电路对容量稳定性要求极高,可优先选用NP0/C0G材质电容。

贱金属电极(BME)技术

传统贵金属电极(如银钯)成本高且高频损耗较大。采用贱金属电极(如镍、铜)可降低电极厚度,减少涡流损耗,同时降低成本。顺络部分产品已应用BME技术,可进一步优化其高频性能。

二、结构设计:多层化与布局优化

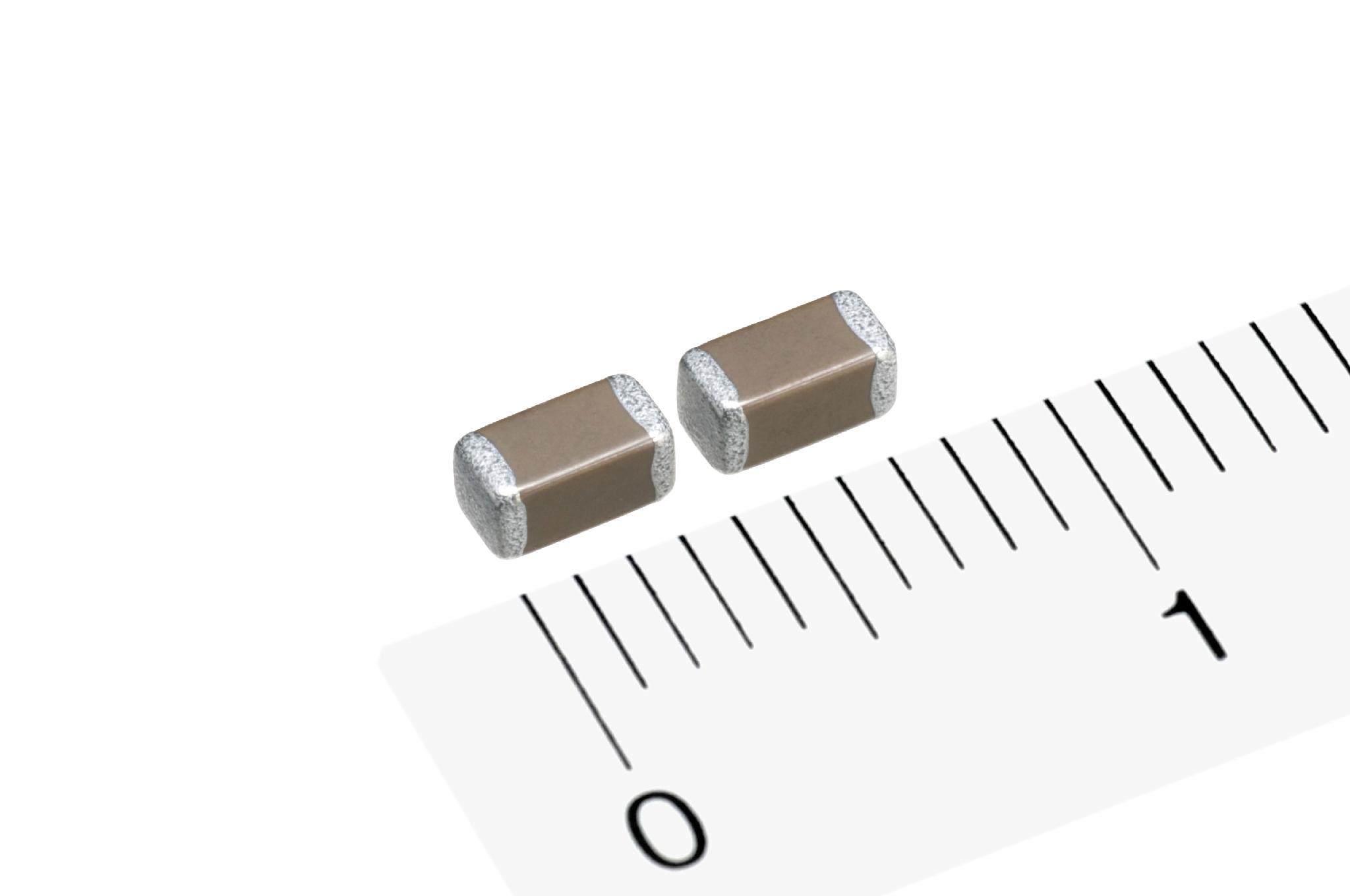

多层陶瓷结构(MLCC)

通过增加陶瓷层数缩短电流路径,降低等效串联电感(ESL)。例如,0201封装MLCC的ESL可控制在0.1nH以内,显著减少高频阻抗。对于1206封装电容,可通过优化内部电极布局(如LW反转型结构)进一步降低ESL,使1μF/6.3V电容的自谐振频率(SRF)超过10GHz。

无引线框设计

传统引线框会引入寄生电感,影响高频性能。采用模塑一体成型技术(如WCX系列)可消除引线框,减少寄生参数,支持-55℃~155℃宽温域应用,解决高温老化问题。

三、工艺控制:低损耗制造流程

低温共烧陶瓷(LTCC)技术

LTCC工艺可实现多层陶瓷与电极的低温共烧,减少介质与电极间的界面损耗,提升高频性能。顺络若采用该技术,可进一步降低电容的介质损耗。

精确控制陶瓷配方与烧结工艺

优化陶瓷介质的晶粒结构与致密度,减少晶界缺陷,可降低介质极化损耗。同时,严格控制烧结温度与时间,避免因过度烧结导致介质性能退化。

四、电路应用:合理布局与匹配

避免靠近高频干扰源

在PCB布局时,将电容远离开关电源、高频数字信号线等干扰源,减少电磁耦合引起的损耗。

并联使用降低ESR

高频电路中,电容的等效串联电阻(ESR)是主要损耗来源之一。可通过并联多个电容(如多个0.1μF电容并联)降低总ESR,从而减少损耗。例如,并联后ESR可降低至单只电容的1/n(n为并联数量)。

选择合适封装与容量

高频电路中,小封装电容(如0402、0201)的ESL更低,适合高频滤波;大容量电容(如1μF以上)的ESR较高,需根据电路需求权衡。对于CC1206KKX7RBBB104(0.1μF),若需进一步降低高频损耗,可考虑替换为0402封装同容量电容。

五、温度管理:散热优化

增加散热面积

在PCB上为电容预留散热焊盘,或采用散热片、热管等辅助散热措施,降低电容工作温度。高温会加剧介质损耗(如X7R电容在85℃时的tanδ比20℃时高50%),因此控制温度是降低损耗的关键。

选用宽温域产品

顺络部分产品支持-55℃~155℃宽温域应用(如WCX系列),若电路工作温度范围较大,可优先选用此类产品,减少温度对损耗的影响。